潘浩林 | Haolin Pan

About

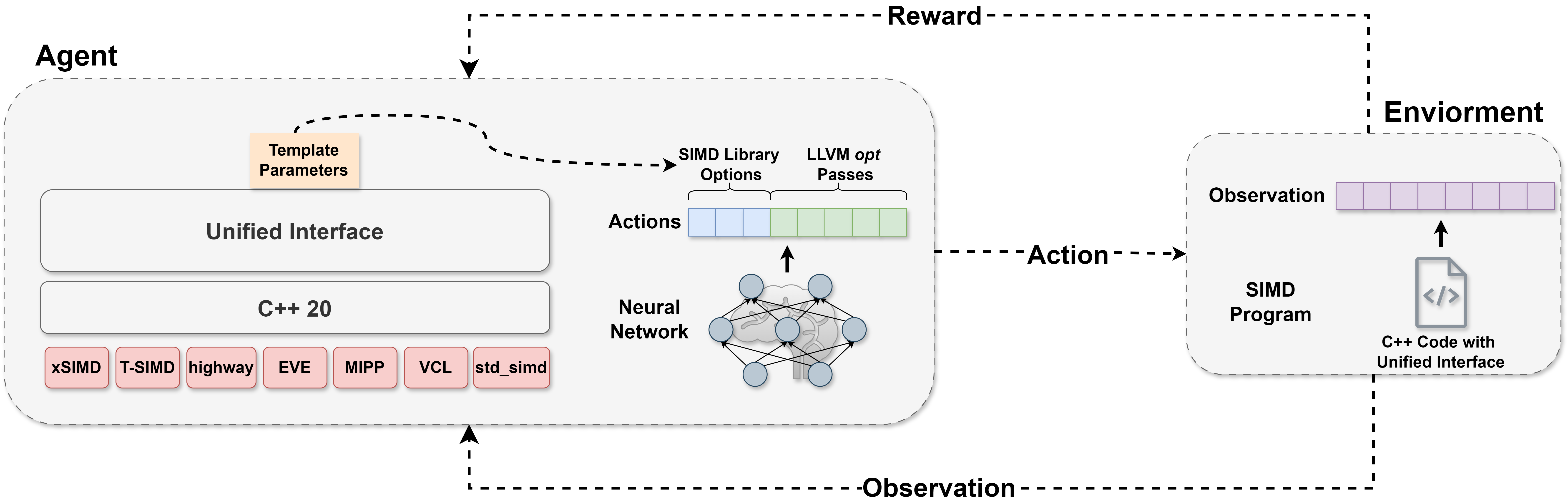

I am 潘浩林 (Haolin Pan), a Ph.D. candidate at the Institute of Software, Chinese Academy of Sciences. My research focuses on AI Infra, compiler optimization, compiler auto-tuning, program representation learning, and SIMD optimization.

I work on building practical AI-for-compiler systems around LLVM / MLIR, including pass-sequence optimization, LLM/RL-driven compiler tuning, quasi-dynamic program representations, and high-performance SIMD library design. My recent work has appeared at NeurIPS, ICLR, ASE, CGO, SEKE, and IEEE TMC. For the latest citation record, please see my Google Scholar profile.

Education & Research

- 2023.09 - 2027.06, Ph.D. in Computer Software and Theory, Institute of Software, Chinese Academy of Sciences.

- 2021.09 - 2023.06, M.Eng. in Electronic Information, Institute of Software, Chinese Academy of Sciences.

- 2016.09 - 2020.06, B.Eng. in Computer Science and Technology, Zhengzhou University.

- Research topics: AI Infra, AI for Compiler, LLVM / MLIR optimization, compiler auto-tuning, program representation learning, reinforcement-learning-based optimization, and SIMD performance engineering.

News

- 🎉 ICLR 2026: First-author paper on behavioral program embeddings was accepted.

- 🎉 IEEE TMC: Paper FlowXpert was accepted by IEEE Transactions on Mobile Computing.

- 🎉 ASE 2025: First-author paper HybridSIMD was accepted.

- 🎉 NeurIPS 2025: First-author paper Compiler-R1 was accepted.

- 🎉 SEKE 2025: First-author paper on SIMD library and compiler co-optimization was accepted.

- 🎉 CGO 2025: First-author paper on synergy-guided compiler auto-tuning was accepted.

Publications

-

IEEE Transactions on Mobile Computing, 2026.

-

arXiv preprint arXiv:2602.00087, 2026.

-

CGO 2025, 614-627.

-

-

arXiv preprint arXiv:2510.13184, 2025.

-

arXiv preprint arXiv:2510.13176, 2025.

-

IEEE/ACM International Conference on Automated Software Engineering, 2025.

Service, Honors & Skills

- Academic service: NeurIPS 2025 Reviewer, NeurIPS 2026 Reviewer, ICLR 2026 LLA Workshop Reviewer, ICASSP 2026 Reviewer.

- Honors: UCAS Outstanding Student Model, UCAS Outstanding Student Cadre, UCAS Merit Student.

- Patents: first inventor of two SIMD-related invention patents on automatic SIMD-library testing and hybrid SIMD-library programming.

- Technical stack: LLVM, MLIR, C/C++, Python, Shell, Linux, compiler passes, vectorization, auto-tuning, and performance evaluation.

Powered by Jekyll and Minimal Light theme.